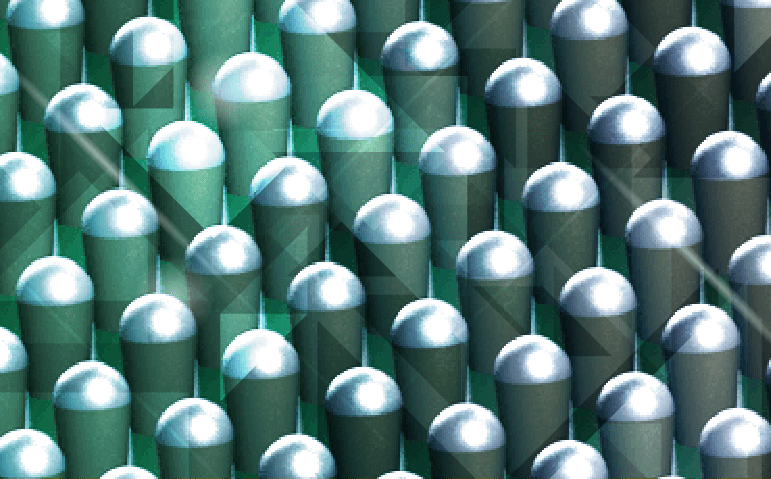

높은밀도,신뢰성및성능을위한 차세대 범프 기술

Copper pillar bump is widely used for many types of flip chip interconnect which offers advantages in many designs while meeting current and future ROHS requirements. It is an excellent interconnect choice for applications such as transceivers, embedded processors, application processors, power management, baseband, ASICs and SOCs where some combination of fine pitch, ROHS/Green compliance, low cost and electromigration performance are required.

Benefits of Copper Pillar

- Fine pitch capable down to 30 μm in-line and 30/60 μm staggered

- Superior electromigration performance for high-current carrying capacity applications

- Cu 필러 범프 전 웨이퍼 레벨에서의 전기적 테스트

- Compatible with bond pad opening/pitch and pad metallization of die designed for wirebond which enables quick time-to-market for conversion to flip chip

- 기판 층 수를 줄임으로써 설계 단계에서의 비용 절감

- 고밀도 범프 설계에 Au 스터드 범프에 비해 저렴한 비용의 미세 피치 Flip chip (FPFC) 접합

- Various Cu pillar structures available from Cu bar type, standard Cu pillar, fine pitch Cu pillar and micro-bumps. Also, available in different stack-ups from Cu+Ni+Pb-free, Cu+Ni+Cu+Pb-free depending upon application requirements

- Available with and without repassivation

- 첨단 실리콘 노드 Low-k 장치에 적합

- 칩과 패키지의 거리를 좁혀 더 작은 풋프린트를 제공하는 언더필의 필렛 크기 축소

- Extreme fine pitch on silicon package down to 30 μm for TSV and CoC

Q & A

앰코에 대해 궁금한 점이 있다면

하단의 ‘문의하기’를 클릭하세요.